# 2023 SEMICON West Technology Breakfast

## Forward-Looking Statements and Other Information

This presentation contains forward-looking statements, including those regarding anticipated growth and trends in our businesses and markets, industry outlooks and demand drivers, technology transitions, the path to net zero and our environmental goals, our investment and growth strategies, our development of new products and technologies, the EPIC Center, our business outlook, and other statements that are not historical facts. These statements and their underlying assumptions are subject to risks and uncertainties and are not guarantees of future performance.

Factors that could cause actual results to differ materially from those expressed or implied by such statements include, without limitation: the level of demand for our products, our ability to meet customer demand, and our suppliers' ability to meet our demand requirements; global economic, political and industry conditions, including rising inflation and interest rates; the implementation and interpretation of new export regulations and license requirements, and their impact on our ability to export products and provide services to customers and on our results of operations; global trade issues and changes in trade and export license policies; our ability to obtain licenses or authorizations on a timely basis, if at all; consumer demand for electronic products; the demand for semiconductors; customers' technology and capacity requirements; the introduction of new and innovative technologies, and the timing of technology transitions; our ability to develop, deliver and support new products and technologies; the concentrated nature of our customer base; our ability to expand our current markets, increase market share and develop new markets; market acceptance of existing and newly developed products; our ability to obtain and protect intellectual property rights in key technologies; our ability to achieve the objectives of operational and strategic initiatives, align our resources and cost structure with business conditions, and attract, motivate and retain key employees; failure to realize the anticipated benefits of our planned investments; construction delays, cost increases or changes in investment or construction plans related to the EPIC Center; the effects of regional or global health epidemics, including COVID-19; acquisitions, investments and divestitures; changes in income tax laws; the variability of operating expenses and results among products and segments, and our ability to accurately forecast future results, market conditions, customer requirements and business needs; our ability to ensure compliance with applicable law, rules and regulations; our ability to achieve environmental, social and governance strategies, commitments and targets; and other risks and uncertainties described in our filings with the U.S. Securities Exchange Commission, including our recent Forms 10-Q and 8-K. All forward-looking statements are based on management's current estimates, projections and assumptions, and we assume no obligation to update them.

Applied Materials, the Applied Materials Logo, and other trademarks so designated as product names are trademarks of Applied Materials, Inc. Other names and brands are the property of third parties.

## Welcome

#### Mike Sullivan Corporate Vice President Investor Relations

7:30 Mike Sullivan Welcome

**7:35 Dr. Prabu Raja** EPIC<sup>™</sup> Opportunities

**7:50 Mike Rice** Vistara<sup>™</sup> and EcoTwin<sup>™</sup>

8:05 Dr. Sundar Ramamurthy Heterogenous Integration (HI)

8:15 Vincent DiCaprio HI Panel

9:00 Adjourn Q&A Mingle

4 Applied Materials External

### **SEMICON West 2023 Themes**

## **\$1T Industry Growth Challenges**

## **Epic Opportunities**

#### Dr. Prabu Raja

President Semiconductor Products Group

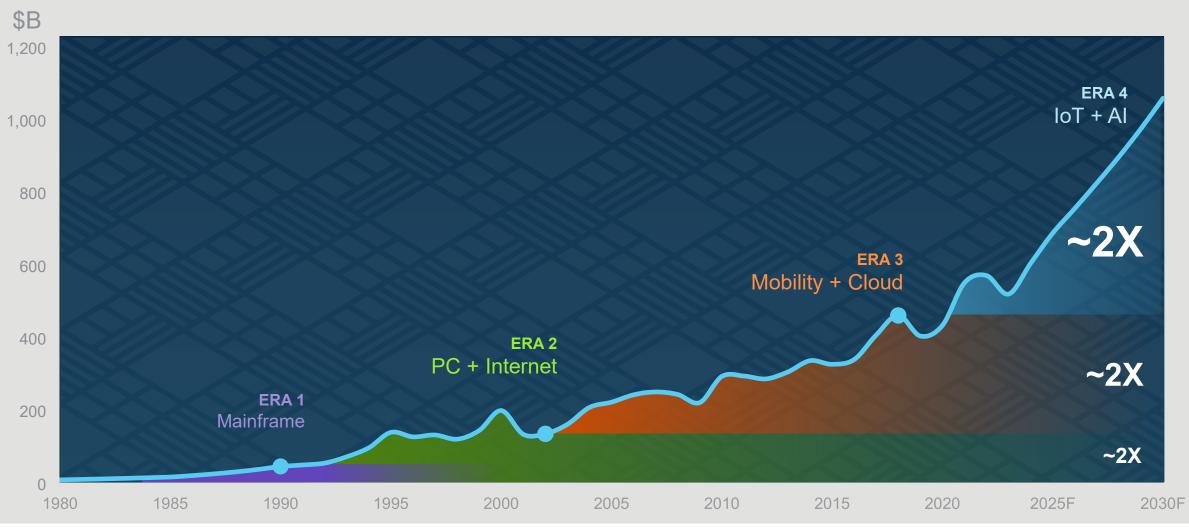

## Path to a \$1T Semiconductor Industry

Source: SIA, Applied Materials - SMI

#### Each computing era ~doubles size of semiconductor market

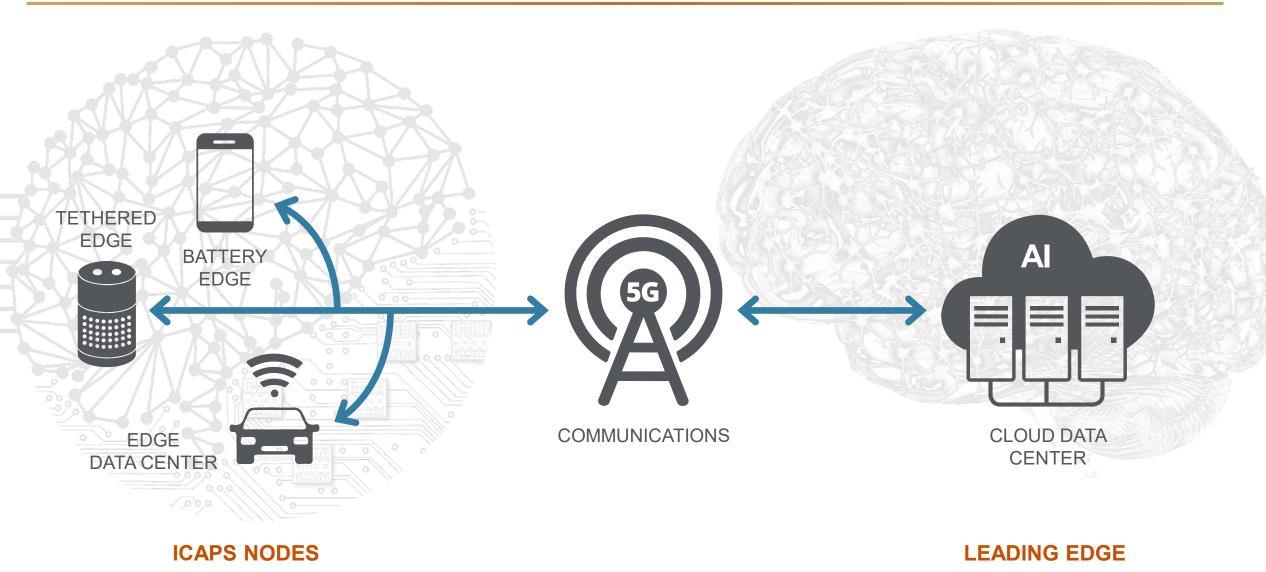

## Internet of Things and Artificial Intelligence Era

## Clean Energy Revolution Needs ICAPS and Leading-Edge Silicon

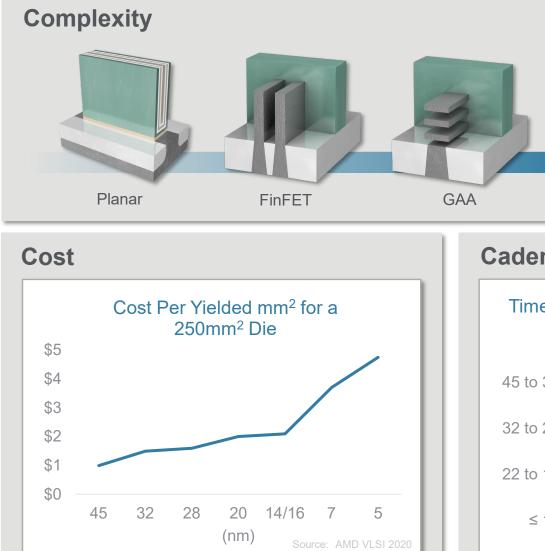

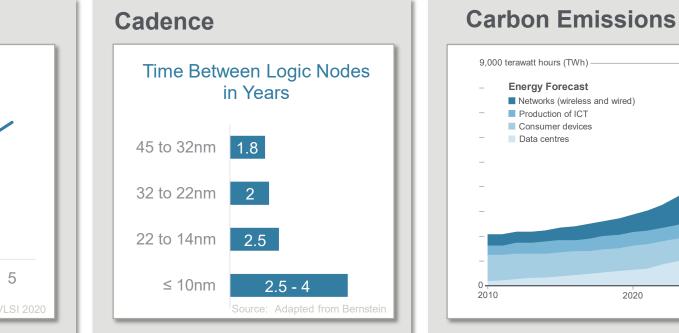

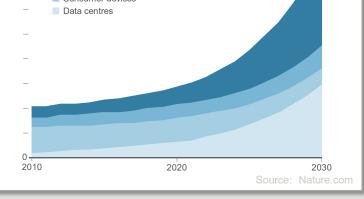

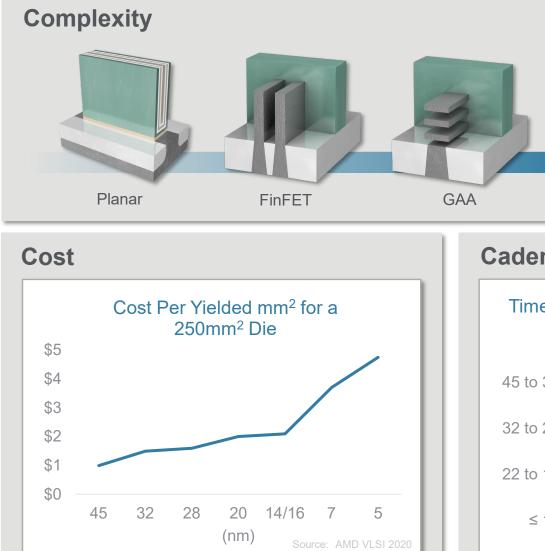

## Significant Challenges Across the Semiconductor Industry

#### **College Grads**

- 1,000,000: additional skilled workers needed by 2030

- 100,000: number of graduate students enrolled in electrical engineering and computer science in the U.S. annually

### 20.9% of projected electricity demand Networks (wireless and wired)

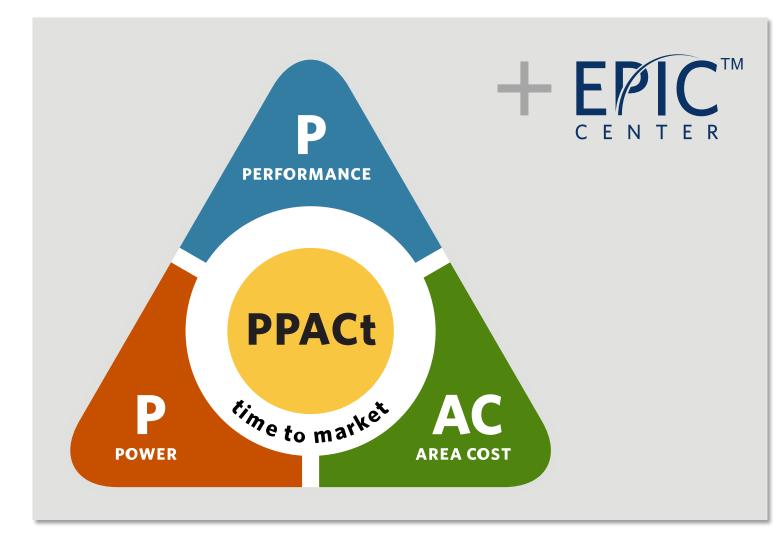

## New Playbook for Innovation and Commercialization

#### **PPACt<sup>™</sup> solutions**

- New materials

- 3D structures

- Atomic-level precision

- Connected capabilities

- System-level innovations

#### **New collaboration models**

- Across industry and academia

- Growing global talent pool

#### Net Zero

Energy efficient semiconductors and manufacturing operations

## **Key Playbook Elements**

# Inclusive innovation to accelerate commercialization

- Equipment and processes → device validation - EPIC<sup>™</sup> Center

- Engineering of technologies → products - Collaborative Engineering Center, India

- Foundational research & talent development - University Innovation Networks, ASU

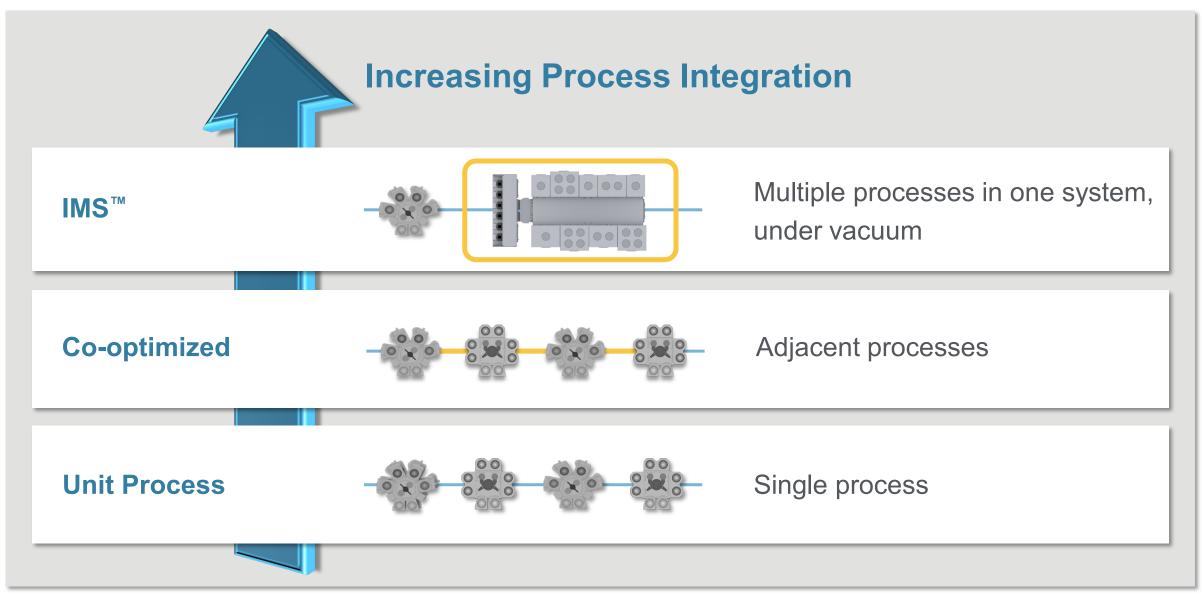

New products for integrated processes

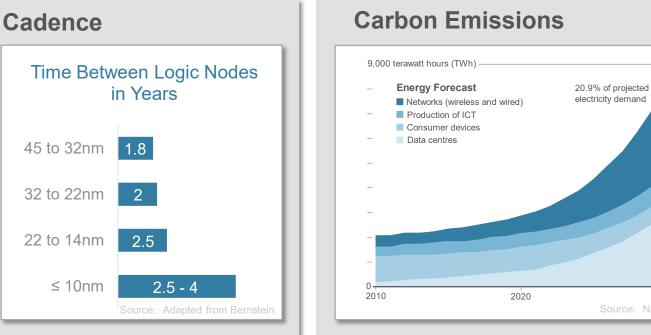

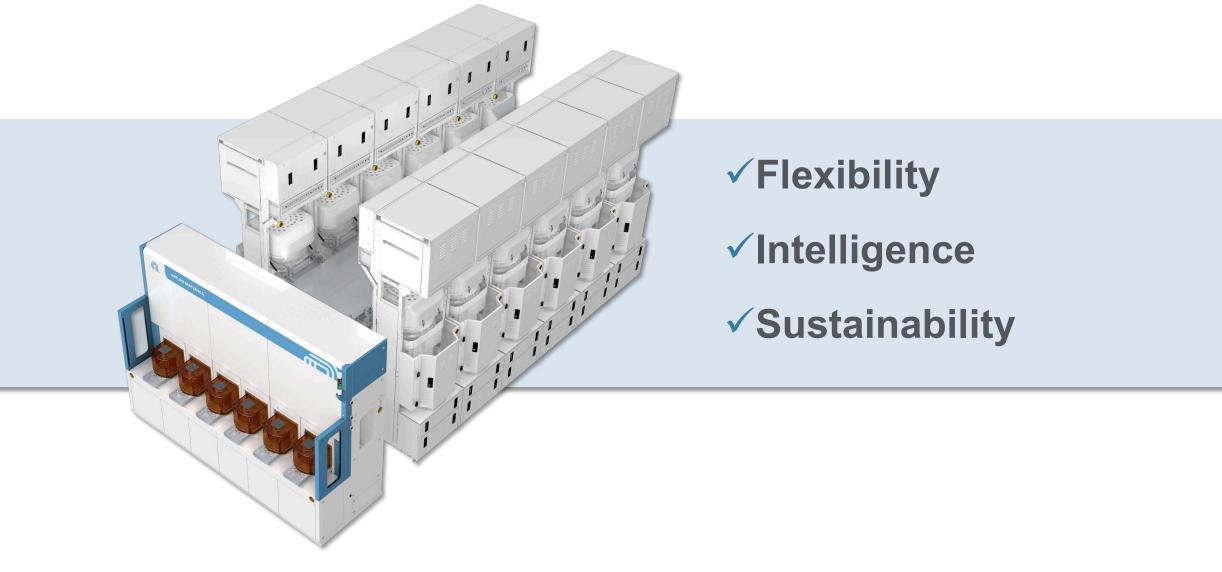

- Flexible, intelligent and sustainable products with greater integration capabilities *Vistara*<sup>™</sup>

- Integrated Materials Solution<sup>®</sup>

- Al<sup>x</sup> Actionable Insight Accelerator<sup>™</sup>

- EcoTwin<sup>™</sup>

#### System-level innovations for PPACt<sup>™</sup> acceleration

System Technology Co-optimization (STCO) - *Heterogeneous Integration*

#### NEW

#

» 180k ft<sup>2</sup> of cleanroom + supporting labs

- » Applied, Customer, University and Partner space

- » Operational Q1'26

#### CURRENT

APPLIED APPLIED

#### MTC R&D Fab

- » 44k ft<sup>2</sup> of cleanroom

- + supporting labs

- » Applied only

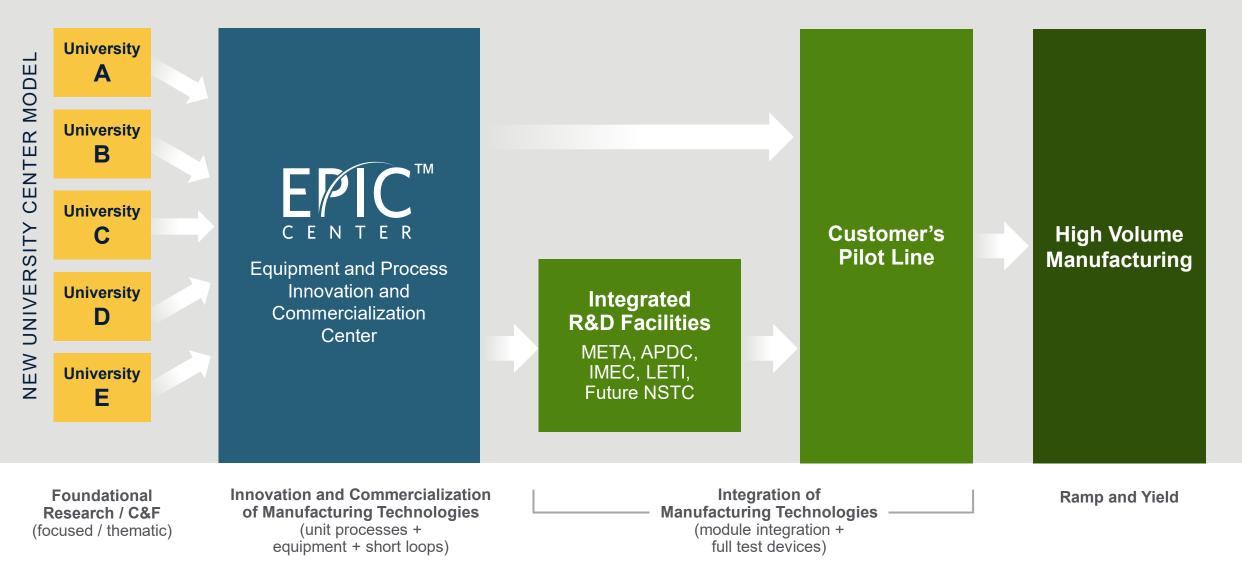

## **EPIC<sup>™</sup> Center Implementation**

\*Conceptual layout only

#### FOR CHIPMAKERS AND INDUSTRY PARTNERS

Co-development and early validation to accelerate new devices and structures

- New materials

- New technologies

- New process flows

#### FOR UNIVERSITIES AND START-UPS

Co-development and early validations on new materials and technologies

- Accelerate commercialization of academic research

- Attract, inspire and train next-generation talent

### Designed for high-velocity innovation and commercialization

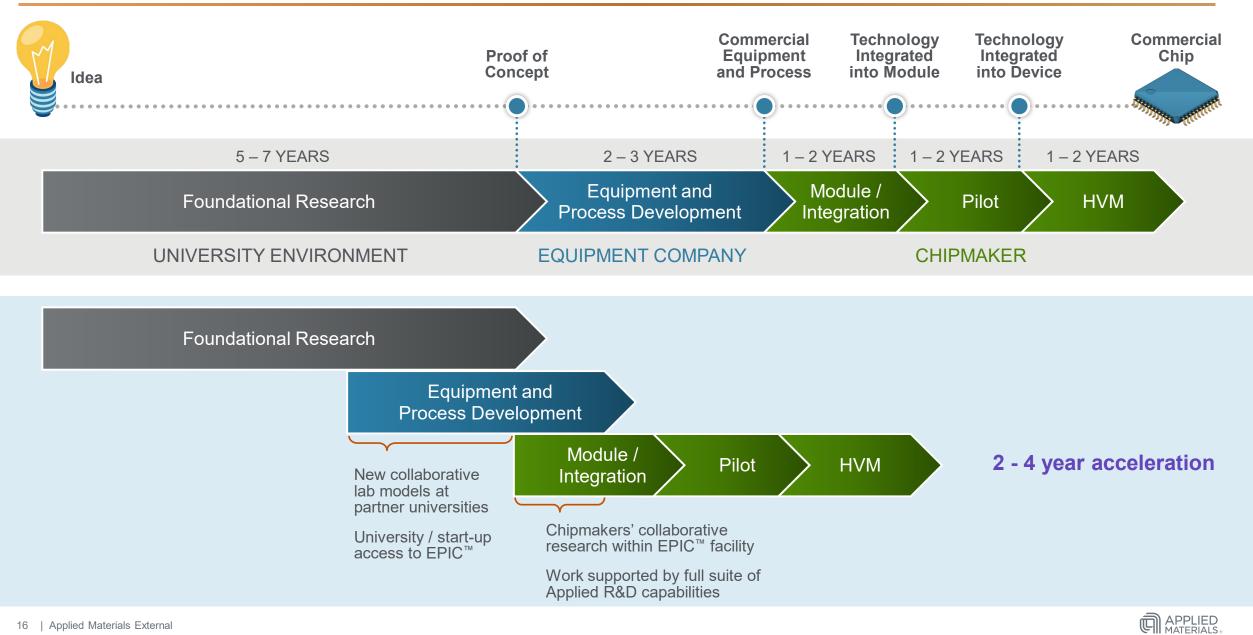

## **New Commercialization Path**

## EPIC<sup>™</sup> University Innovation Network

## New collaboration models to accelerate commercialization of innovations

- World-class shared R&D and prototyping facilities

- Access to industry partners, startups and government entities

- Talent development through hands-on learning and research

Foundational Research

#### UNIVERSITY ENVIRONMENT

Equipment and Process Development

EQUIPMENT COMPANY

Foundational Research / C&F (focused / thematic) Innovation and Commercialization of Manufacturing Technologies (unit processes + equipment + short loops)

University Innovation Network: Materials-to-Fab Center

Press Release

#### ARIZONA STATE UNIVERSITY AND APPLIED MATERIALS TO CREATE 'MATERIALS-TO-FAB' CENTER AT ASU RESEARCH PARK

More than \$270 million in corporate and state investment will help advance Arizona's semiconductor industry

**TEMPE, Arizona and SANTA CLARA, Calif.,** – Arizona State University (ASU) and Applied Materials, Inc. today announced an alliance, aided by the Arizona Commerce Authority, that brings more

## ARIZONA STATE UNIVERSITY

## **Key Playbook Elements**

# Inclusive innovation to accelerate commercialization

- Equipment and processes → device validation - EPIC<sup>™</sup> Center

- Engineering of technologies → products - Collaborative Engineering Center, India

- Foundational research & talent development - University Innovation Networks, ASU

New products for integrated processes

- Flexible, intelligent and sustainable products with greater integration capabilities *Vistara*<sup>™</sup>

- Integrated Materials Solution<sup>®</sup>

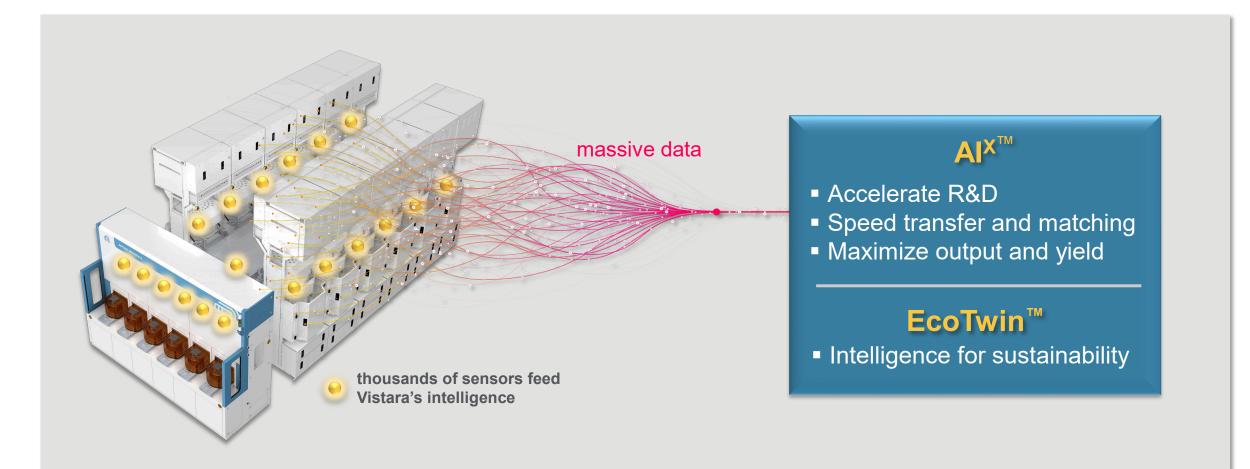

- Al<sup>x</sup> Actionable Insight Accelerator<sup>™</sup>

- EcoTwin<sup>™</sup>

#### System-level innovations for PPACt<sup>™</sup> acceleration

System Technology Co-optimization (STCO) - *Heterogeneous Integration*

## Introducing Vistara<sup>™</sup>

#### Mike Rice

Corporate Vice President, Semiconductor Products Group Applied Materials Fellow

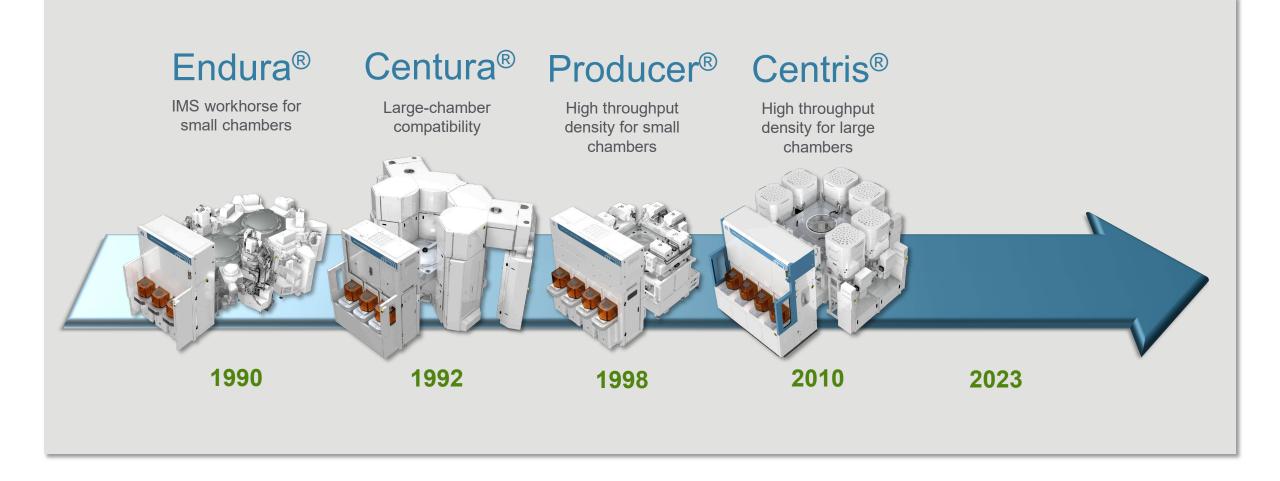

## A Long History of Successful Platforms

## Significant Challenges Across the Semiconductor Industry

#### **College Grads**

- 1,000,000: additional skilled workers needed by 2030

- 100,000: number of graduate students enrolled in electrical engineering and computer science in the U.S. annually

Source: Deloitte

####

2030

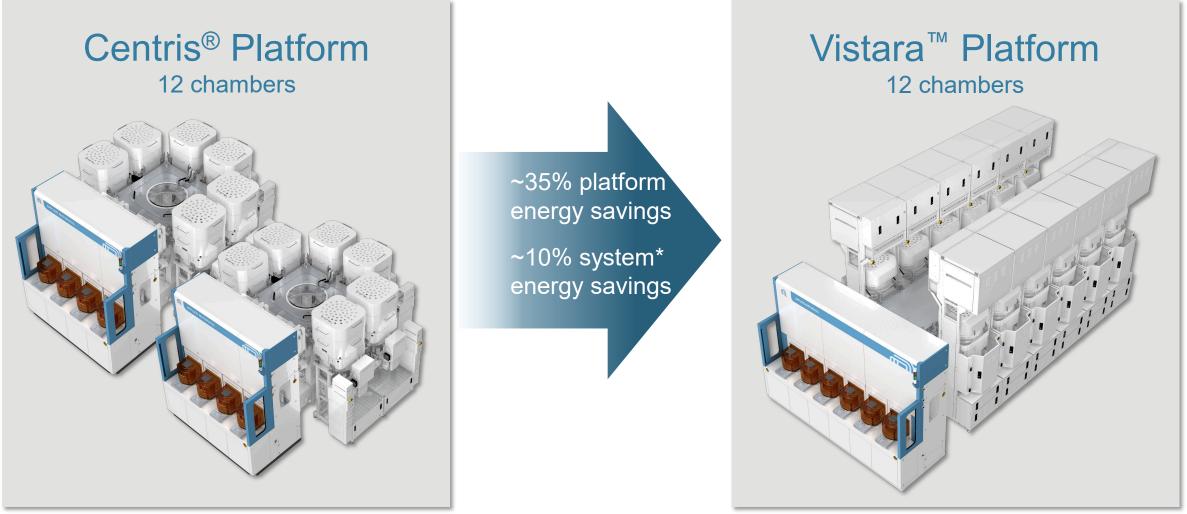

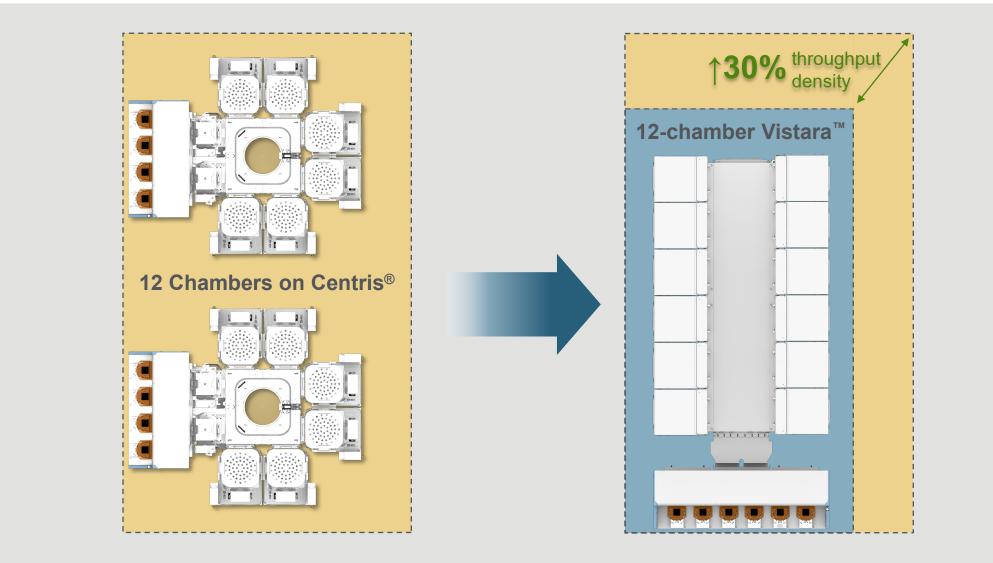

## Introducing the Applied Vistara<sup>™</sup> Platform

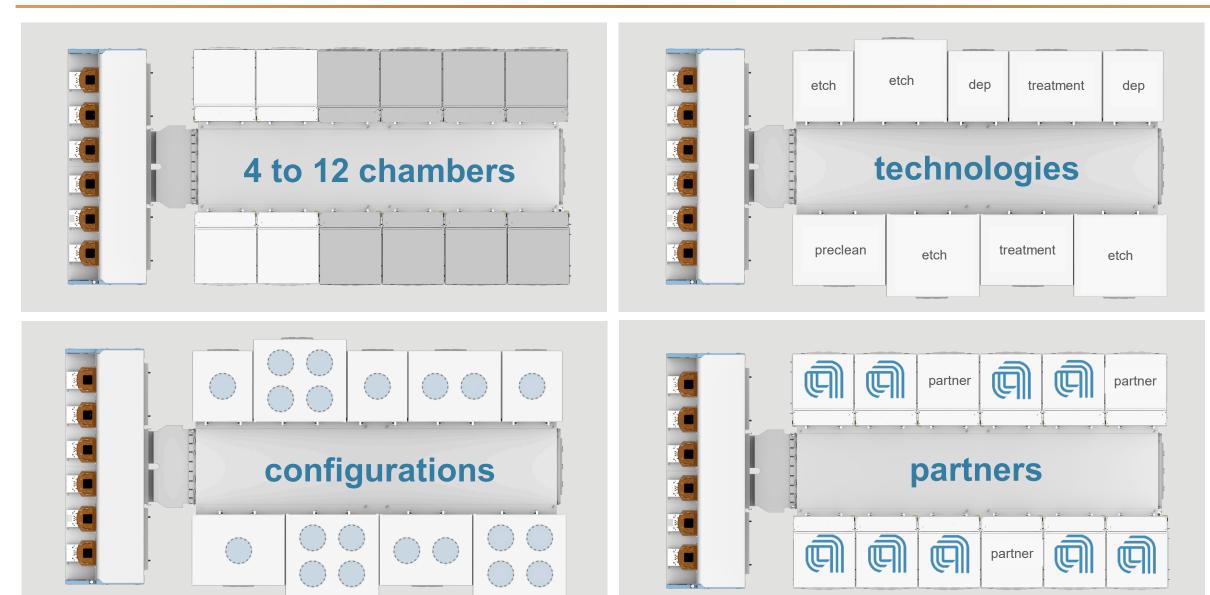

## Vistara<sup>™</sup> Platform Chamber Flexibility

## A Flexible Platform for IMS<sup>™</sup> Connected Capabilities

## Vistara<sup>™</sup> Platform Intelligence

# Accelerating time to market and maximizing ROI and sustainability across the entire lifecycle

### Make Possible a Better Future

ecoJP™ **Sustainability Initiative** 3x30 Goal ↓30% Equivalent Energy ↓30% Chemical Consumption ↓30% Cleanroom Area per Wafer by 2030

## Vistara<sup>™</sup> Platform Energy Savings

\* Systems configured for Sym3 Etch chambers

## Vistara<sup>™</sup> Footprint Savings

## Introducing EcoTwin<sup>™</sup> Eco-Efficiency Software

- Compare resource consumption of different recipes to optimize sustainability

- Monitor energy and gases in real-time to assess environmental impact of chambers, platform and sub-fab components

- Report continuous improvements in environmental performance

#### Demonstrated >30% reduction in CO<sub>2</sub>/wafer in a memory etch application

## The most flexible IMS-ready platform!

## **Key Playbook Elements**

# Inclusive innovation to accelerate commercialization

- Equipment and processes → device validation - EPIC<sup>™</sup> Center

- Engineering of technologies → products - Collaborative Engineering Center, India

- Foundational research & talent development - University Innovation Networks, ASU

New products for integrated processes

- Flexible, intelligent and sustainable products with greater integration capabilities *Vistara*<sup>™</sup>

- Integrated Materials Solution<sup>®</sup>

- Al<sup>x</sup> Actionable Insight Accelerator<sup>™</sup>

- EcoTwin<sup>™</sup>

#### System-level innovations for PPACt<sup>™</sup> acceleration

System Technology Co-optimization (STCO) - *Heterogeneous Integration*

## **Heterogenous Integration**

#### Dr. Sundar Ramamurthy

Group Vice President Heterogenous Integration, ICAPS and Epitaxy Semiconductor Products Group

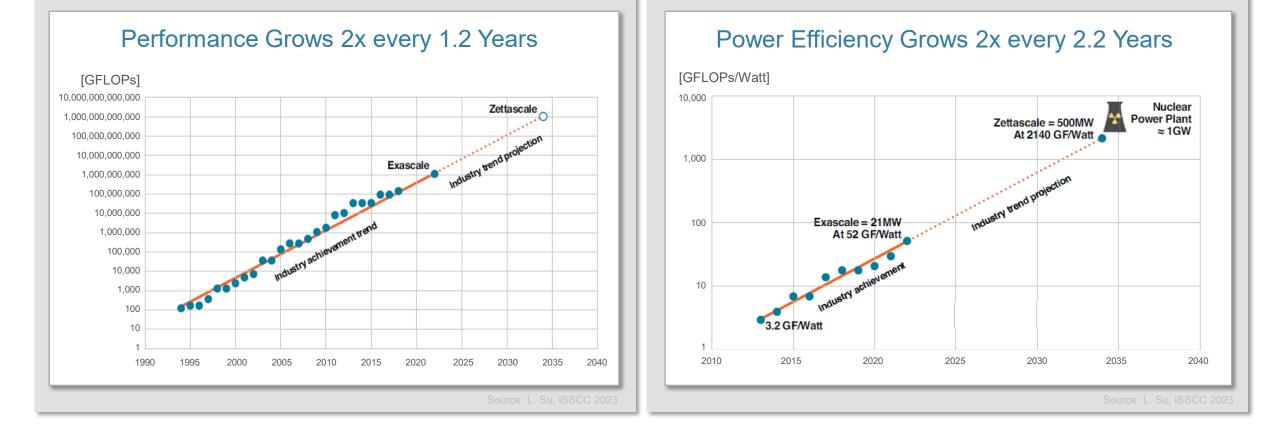

## **Performance Outpacing Power Efficiency**

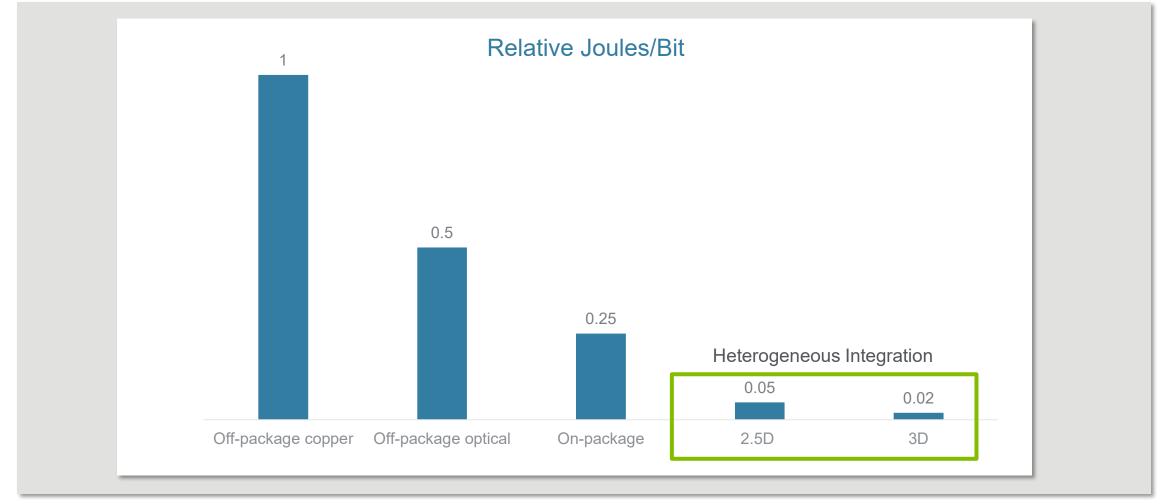

## Heterogeneous Integration Reduces Power

Source: Adapted from L. Su, ISSCC 2023

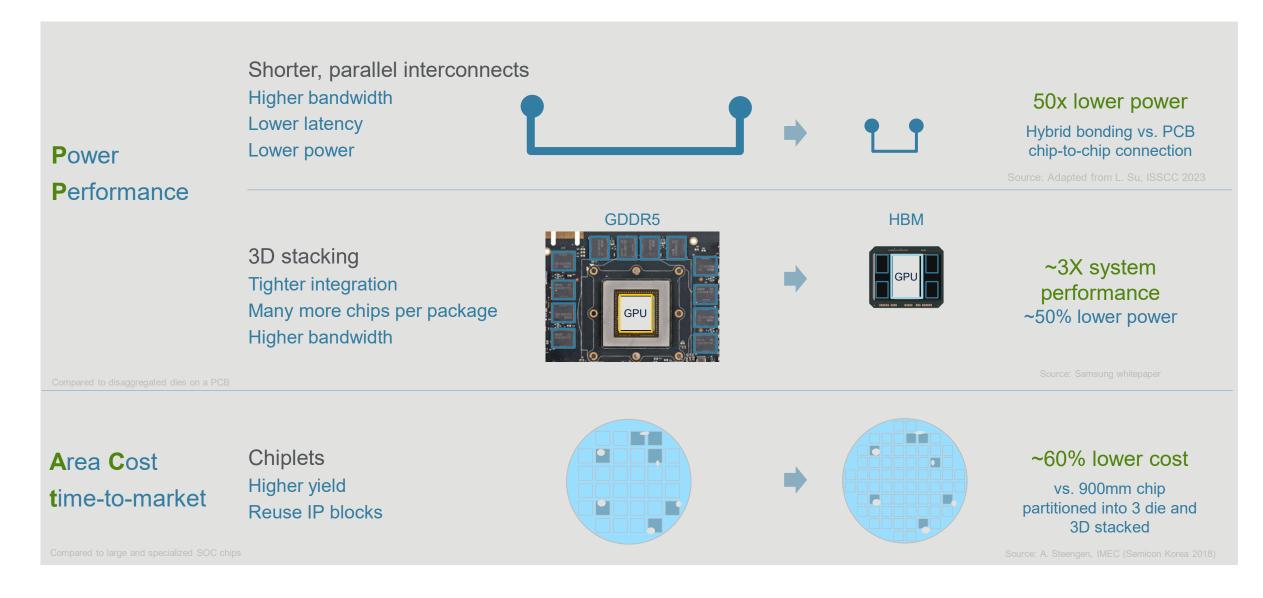

#### Heterogeneous Integration Improves PPACt<sup>™</sup>

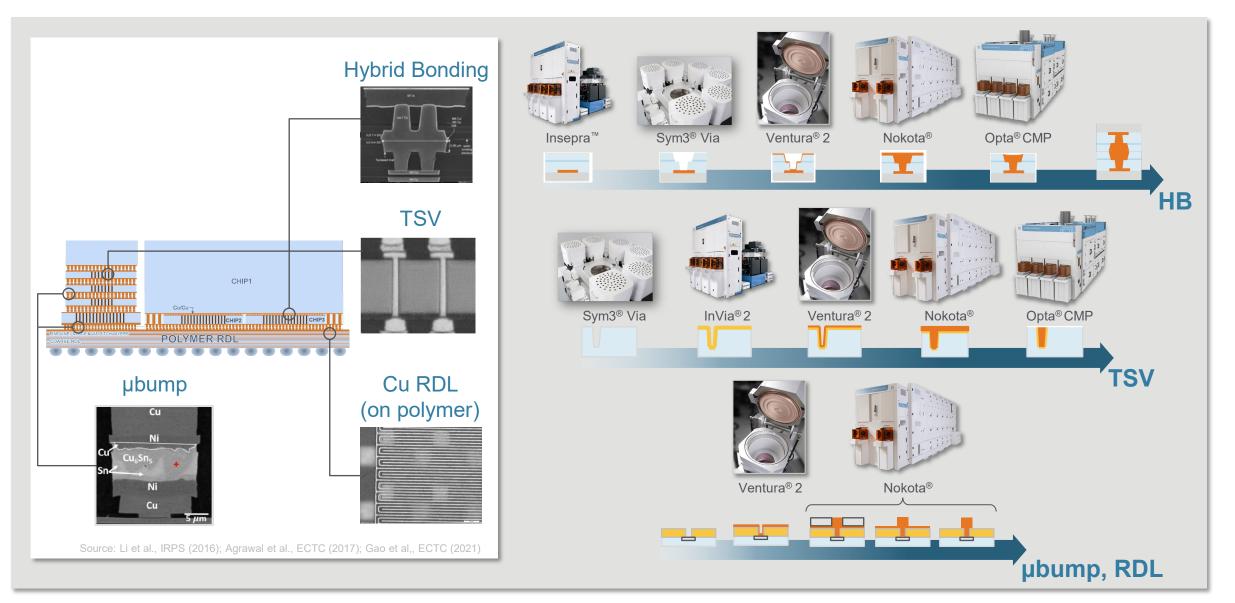

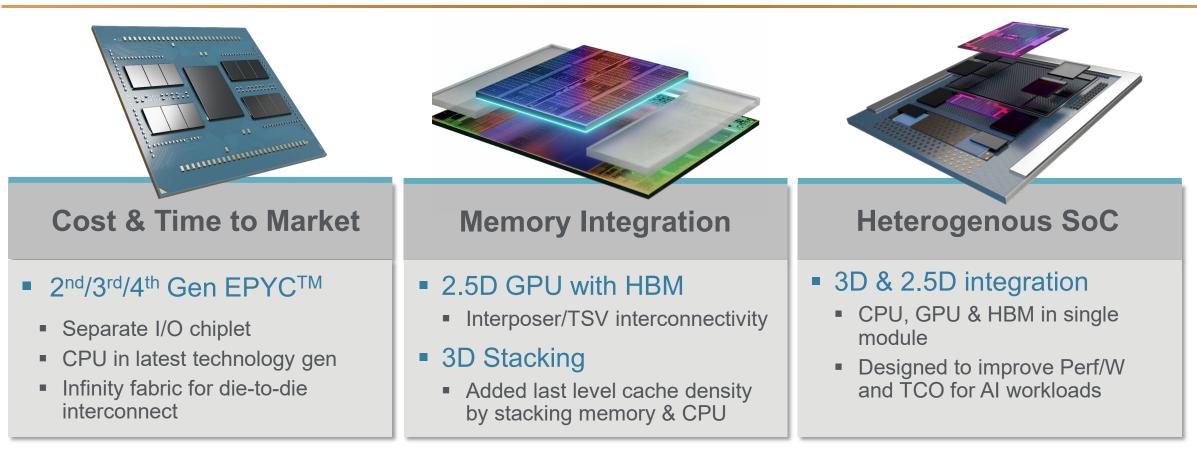

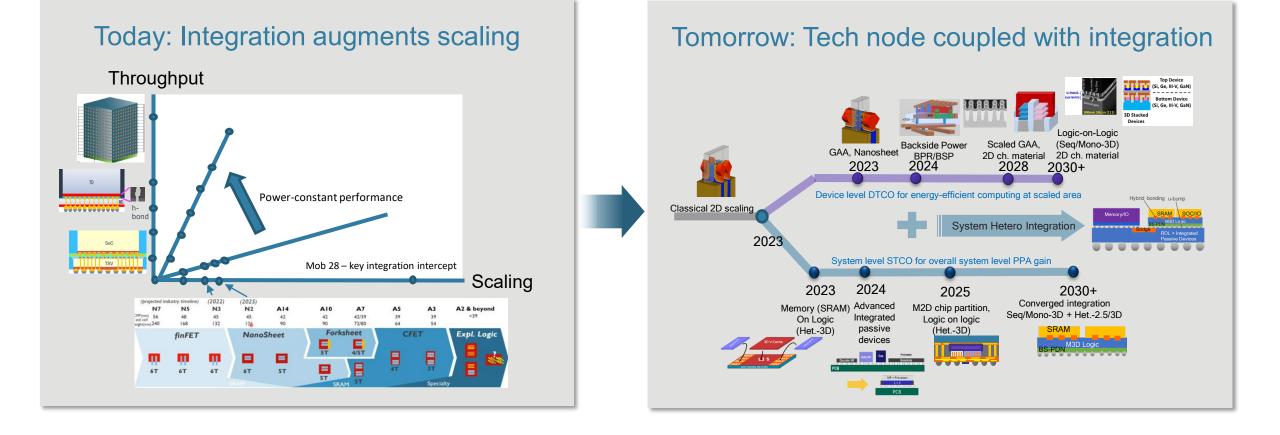

### System-Level Integration with 2D and 3D Heterogeneous Integration

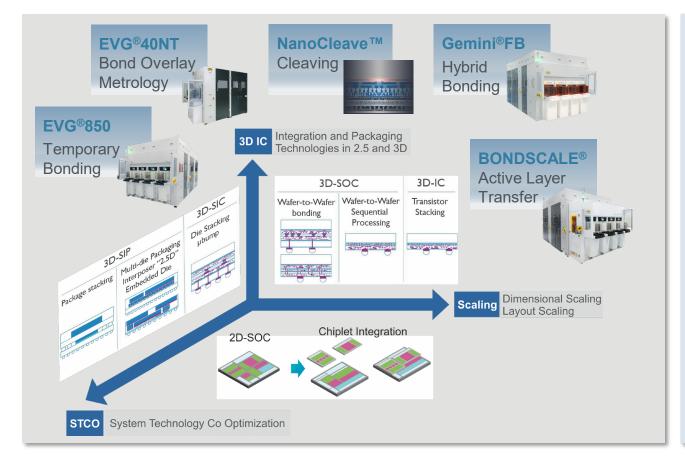

#### **New Products Enable Heterogeneous Integration**

### Key Playbook Elements for Heterogenous Integration

Advanced Packaging Development Center for Heterogeneous Integration Integrated Materials Solution<sup>®</sup> for Die-to-Wafer Hybrid Bonding Industry Enablement of 2.5D and 3D IC Packaging Solutions

## **Heterogenous Integration Panel**

#### Vincent DiCaprio

Vice President, Business and Corporate Development Heterogeneous Integration and ICAPS Semiconductor Products Group

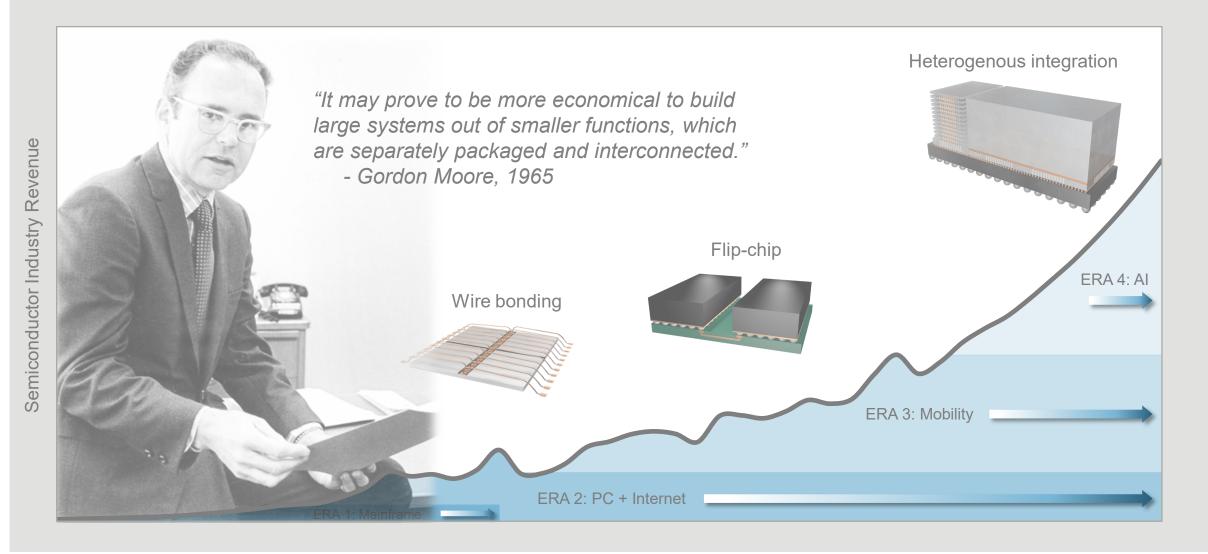

### Heterogeneous Chip Design – An Evolution of Moore's Law

Source: SEMI, VLSI, Applied Materials https://archive.computerhistory.org/resources/access/text/2017/03/102770822-05-01-acc.pdf

PC: Personal Computer Al: Artificial Intelligence

# **Heterogenous Integration Panel**

**Mark Fuselier**

SVP of Technology and Product Engineering

AMD

Babak Sabi SVP of Assembly Test Technology Development Intel

PR "Chidi" Chidambaram VP of Engineering Qualcomm

Richard Blickman Founder and CEO

Besi

Paul Lindner Executive Technology Director EV Group

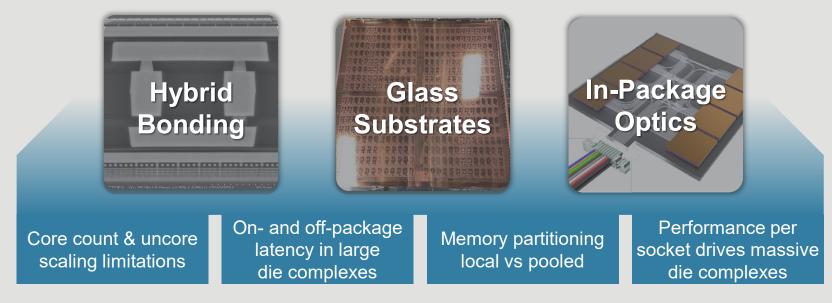

#### **Enabling Faster Scale of Compute Capability**

#### **Evolution of the Heterogeneous Roadmap**

Qualcom

#### Vision of the Future for AI/HPC

Advanced packaging enables high density interconnects with larger die complexes from multiple process nodes

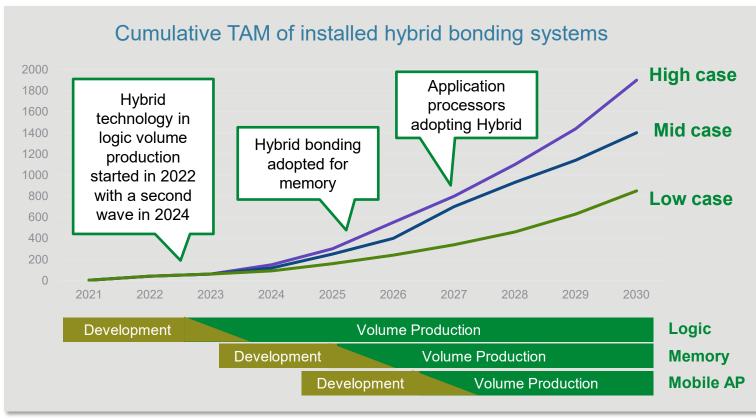

## **Estimated Hybrid Bonding Market Development**

Source: Besi estimates, June 2023 Cases based on potential adoption scenarios

#### Estimated 800 – 1,900 systems cumulative by 2030

- Logic device production and adoption continues

- Technology adoption coming in waves

- Major memory companies engaged

- Starting programs for HBM4 Hybrid packages

- Increased interest for HB usage in consumer applications

#### Changes to market forecast vs. CMD '22

- Upside and low case unit potential expanded

- Tracking to mid case currently

- Higher ASPs anticipated due to higher accuracy requirements post 2024

#### **Expected rollout sequence:**

- Logic

- Memory

- Mobile

- Other Applications

## Wafer Bonding is a Scaling Booster

- Wafer Bonding

- » Complements the traditional dimensional scaling

- Wafer-to-Wafer Hybrid Bonding:

- » Enables higher functional density at the wafer level back end

- Active Layer Transfer Fusion Bonding:

- » Exploits the wafer back side and enables front end transistor level stacking